चिपलेट्स का आगमन • लेख • ज्ञान का उत्साह, 3 डी आईसी विषम एकीकरण के लिए चिपलेट डिजाइन किट | सीमेंस सॉफ्टवेयर

3 डी आईसी विषम एकीकरण के लिए मार्ग प्रशस्त करने में मदद करने के लिए चिपलेट डिज़ाइन किट का उपयोग करना

Contents

- 1 3 डी आईसी विषम एकीकरण के लिए मार्ग प्रशस्त करने में मदद करने के लिए चिपलेट डिज़ाइन किट का उपयोग करना

- 1.1 चिपलेट्स का आगमन

- 1.2 प्रस्तावना

- 1.3 चिपलेट, क्यूसैको ?

- 1.4 चिपलेट के आर्थिक पहलू

- 1.5 दो उदाहरण: AMD और INTEL (ALTERTA)

- 1.6 3 डी आईसी विषम एकीकरण के लिए मार्ग प्रशस्त करने में मदद करने के लिए चिपलेट डिज़ाइन किट का उपयोग करना

- 1.7 सफल 2 के लिए एक पारिस्थितिकी तंत्र का निर्माण.5 डी और 3 डी चिपलेट मॉडल एकीकरण

- 1.8 सफल 2 के लिए एक पारिस्थितिकी तंत्र का निर्माण.5 डी और 3 डी चिपलेट मॉडल एकीकरण

- 1.9 लीक हुई छवि से GPU AMD Radeon के लिए चिपलेट के एक महत्वाकांक्षी डिजाइन का पता चलता है

- 1.10 लीक हुई छवि से GPU AMD Radeon के लिए चिपलेट के एक महत्वाकांक्षी डिजाइन का पता चलता है

कुछ साल बाद, पहले प्रोसेसर विशेष रूप से इंटेल 4004 के साथ दिखाई दिए, आज अपेक्षाकृत सरल. तब प्रोसेसर अधिक जटिल हो गए.

चिपलेट्स का आगमन

JZDS और डिस्कोर्ड पर एक चर्चा के बाद, मैंने खुद से कहा कि चिपलेट्स पर एक लेख लिखना सबसे बड़ी संख्या के लिए फायदेमंद होगा. और JZDS के साथ क्या हो सकता है के विपरीत एक लिखित ट्रैक रखेगा

बहुत लंबा टिकट लिखने के बजाय, मैंने विवरण में थोड़ा और प्राप्त करने के लिए लेख के प्रारूप को प्राथमिकता दी. मुझे उम्मीद है कि आपको यह सिखाने में सक्षम होगा कि चिपलेट क्या हैं, यह तकनीक क्यों बनाई गई थी और आने वाले वर्षों में यह क्यों विकसित होगा.

- प्रस्तावना

- चिपलेट, क्यूसैको ?

- चिपलेट के आर्थिक पहलू

- दो उदाहरण: AMD और INTEL (ALTERTA)

प्रस्तावना

यह लेख कंप्यूटर, इलेक्ट्रॉनिक और आर्किटेक्चर अवधारणाओं के बारे में बात करता है जो कुछ पाठकों के लिए पर्याप्त रूप से उन्नत हो सकते हैं. मैं आपको इस प्रस्तावना में थोड़ा लोकप्रियता प्रदान करता हूं कि हम थोड़ा बेहतर समझने के लिए कि हम किस बारे में बात कर रहे हैं.

शुद्धतावादियों के लिए, शॉर्टकट बनाए जाएंगे, यह लोकप्रियकरण समझ को सुविधाजनक बनाने के लिए स्वेच्छा से जानकारी निभाने में सक्षम हो सकता है.

चिपलेट, क्यूसैको ?

आइए सबसे कठिन के साथ शुरू करें, परिभाषित करें कि एक चिपलेट क्या है !

वास्तव में चिपलेट शब्द 1970 के दशक में दिखाई दिया, लेकिन इसका उपयोग मुख्य रूप से हाल के वर्षों में बंद हो गया है, उन लोगों के लिए जो जटिल प्रोसेसर या इलेक्ट्रॉनिक चिप्स जैसे कि एफपीजीए (चिप्स जिनके आंतरिक तार्किक दरवाजे को फिर से बनाया जा सकता है) में रुचि रखते हैं). दूसरों के लिए, कमरे के निचले भाग में, आपने इस शब्द के बारे में कभी नहीं सुना होगा, हम इसे उपाय करेंगे !

आइए एक इलेक्ट्रॉनिक चिप क्या है के आधार पर वापस जाएं: उत्कीर्ण सिलिकॉन (प्रसिद्ध ट्रांजिस्टर) का एक टुकड़ा जो एक मामले में एनकैप्सुलेटेड है. क्रॉसिंग घटकों के साथ, छोटे सोना या चांदी के धागे घटक के पैरों को सिलिकॉन के टुकड़े से जोड़ते हैं. शुरुआत में, चिप्स काफी मोटे संकल्पों (आज की तुलना में) के साथ उत्कीर्ण ट्रांजिस्टर से बने होते हैं और कार्य काफी बुनियादी थे: तार्किक दरवाजे, परिचालन एम्पलीफायरों, आदि।. हालांकि, यह पहले से ही मामूलीकरण के संदर्भ में भारी प्रगति थी !

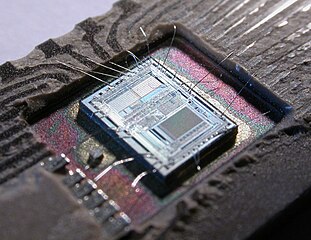

उस समय घटकों में पैर पार थे और सिलिकॉन चिप को इन पैरों से जोड़ना आवश्यक है. यह चांदी या सोने के पतले बेटों के साथ बनाया जाता है जो कि केस के अंदर चिप और पैरों के बीच वेल्डेड होते हैं.

कुछ साल बाद, पहले प्रोसेसर विशेष रूप से इंटेल 4004 के साथ दिखाई दिए, आज अपेक्षाकृत सरल. तब प्रोसेसर अधिक जटिल हो गए.

1970 के दशक से, आईबीएम ने एमसीएम घटक विकसित किए (बहु-चोडु) एक ही मामले में कई सिलिकॉन चिप्स सहित. लेकिन यह तकनीक मुख्य रूप से 90 के दशक के अंत में विकसित होगी. हम 1995 में जारी इंटेल के पेंटियम प्रो को नोट कर सकते हैं. इस प्रोसेसर में दो सिलिकॉन चिप्स शामिल थे: एक प्रोसेसर के लिए सख्ती से बोल रहा था और दूसरा एल 2 कैश मेमोरी (प्रोसेसर और रैम के बीच एक बफर मेमोरी, बहुत तेजी से लेकिन बहुत अधिक महंगा क्योंकि प्रोसेसर के साथ उत्कीर्ण).

जैसा कि हम फोटो में देख सकते हैं, दो चिप्स का आकार लगभग एक ही है और इंटेल ने कैश L2 के कई आकारों की पेशकश की. कैश मेमोरी प्रोसेसर को अलग करने का लाभ मामले में एक अलग आकार की चिप डालकर विभिन्न कैश मेमोरी आकार की पेशकश करते हुए प्रोसेसर चिप पर पैमाने को बचाने में सक्षम होना था.

इस प्रकार का घटक अपेक्षाकृत अविकसित रहता है, भले ही आईबीएम ने एमसीएम घटकों को विकसित करना जारी रखा. 2004 में जारी IBM के Power5 पर ध्यान दें जो चार प्रोसेसर को कैश L3 मेमोरी चिप के साथ देखता है. मामले के अंदर fleas का परस्पर संबंध किया जाता है.

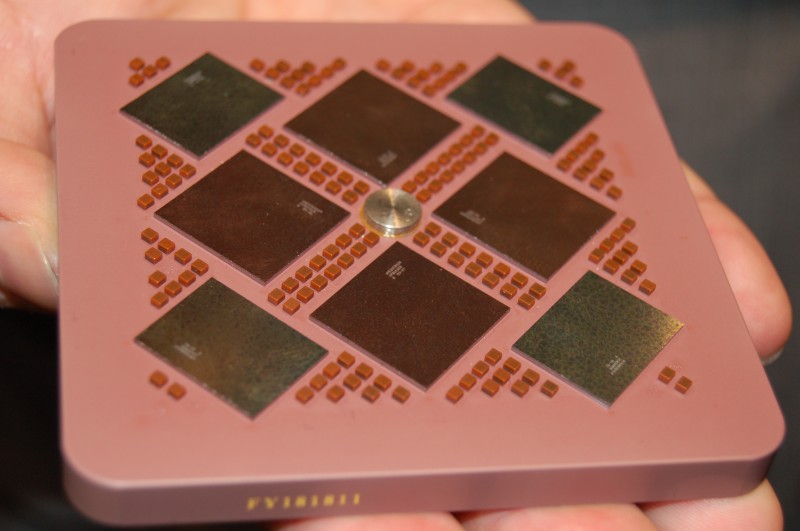

आज प्रौद्योगिकी विकसित हुई है और एमसीएम चिप्स एएमडी प्रोसेसर के साथ उपभोक्ता उत्पादों में मौजूद हैं. यहां हम एक EPYC 7702 प्रोसेसर (अगस्त 2019 में जारी) को 9 परस्पर सिलिकॉन चिप्स से बना देख सकते हैं: 8 चिप्स जिसमें कोर और कैश मेमोरी और अन्य 8 को जोड़ने वाला एक केंद्रीय चिप है और जो डीडीआर के साथ -साथ सिग्नल डी ‘प्रवेश द्वार/ का प्रबंधन करता है। निकास (SATA, PCI EXPRENS, USB, ETC.)).

लेकिन मुझे बताओ जमी, एक चिपलेट क्या है ?

आह हाँ, मैं थोड़ा प्राप्त हुआ

वास्तव में एक चिपलेट एक एमसीएम में मौजूद सिलिकॉन चिप्स में से एक है. एक चिपलेट को अन्य चिपलेट्स के साथ परस्पर जुड़ा किया जाता है. हाँ, यह अपेक्षाकृत सरल है, लेकिन आपको समझने के लिए कुछ अच्छी तस्वीरें दिखाने थीं

फिर भी चिपलेट के अर्थ पर थोड़ा अधिक सटीक होने के लिए, विचार जरूरी नहीं कि कई अलग -अलग चिप्स को एक साथ रखा जाए. जेनेरिक चिप की एक धारणा भी है जिसे पुन: उपयोग किया जा सकता है और एक विशेष प्रोसेसर संदर्भ के लिए समर्पित नहीं है.

चिपलेट के आर्थिक पहलू

छवि के दौरान इस परिचय के बाद, अब हम समझते हैं कि भविष्य में चिपलेट क्यों विकसित होंगे. ऐसा करने के लिए, इलेक्ट्रॉनिक fleas के निर्माण की प्रक्रिया पर लौटना आवश्यक है.

एक आर्मचेयर में आराम से बैठें क्योंकि रेतीले समुद्र तट से यात्रा लंबी होगी

नहीं रुको !

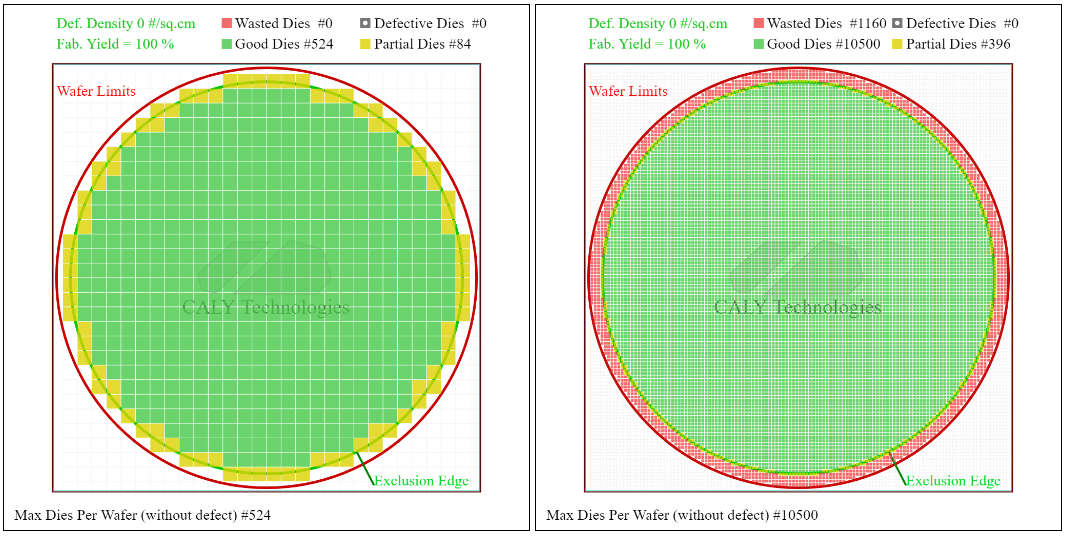

हम सिलिकॉन के निर्माण का एक पूरा हिस्सा खर्च करेंगे. हमें क्या दिलचस्पी होगी पिस्सू का वितरण (मरना) सिलिकॉन केक पर (वफ़र) और विशेष रूप से उकेरने में वृद्धि के साथ उपज का विकास.

लेकिन उपज के इस पहलू से पहले, हमें मरने के अधिकतम भौतिक आकार के बारे में बात करनी चाहिए. दरअसल, एक सिलिकॉन पैनकेक पर एक चिप का एक ही डिजाइन कई बार दोहराया जाता है (दसियों या सौ बार). इस डिजाइन की छाप वैकल्पिक रूप से पराबैंगनी प्रकाश के माध्यम से की जाती है. हालाँकि, लेंस और ऑप्टिकल मैकेनिज्म का एक पूरा सेट है जो पूरे सिलिकॉन केक पर एक ही मरने को रोकता है.

जितना अधिक हम पिस्सू को जटिल करते हैं, उतना ही हम ट्रांजिस्टर डालना चाहते हैं, इसलिए हमें या तो चिप के आकार को बढ़ाना चाहिए, या एक ही सतह में अधिक ट्रांजिस्टर फिट करने के लिए उत्कीर्णन की नाजुकता बढ़नी चाहिए. लेकिन वहाँ भी अन्य बाधाओं और सीमाएं महसूस की जाती हैं.

यही कारण है कि चिपलेट का सिद्धांत इन सीमाओं को बायपास करने के लिए दिलचस्प है: एक अधिक जटिल चिप बनाने के लिए एक साथ जुड़े कई छोटे सिलिकम चिप्स का उपयोग करें लेकिन एक अखंड तरीके से उत्कीर्णन करना असंभव है.

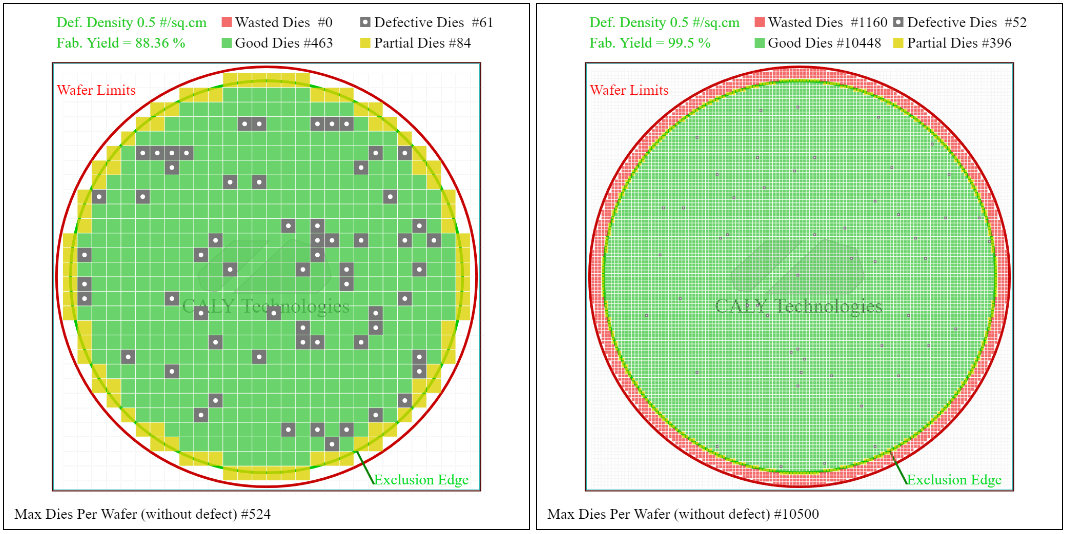

अब वापस उपज के लिए (उपज अंग्रेजी में). सबसे पहले, वेफर्स आकार में गोल हैं और हम इसे आयताकार चिप्स के साथ उकेरना चाहते हैं. पूरे सिलिकॉन का उपयोग नहीं किया जाता है. लेकिन छोटे किनारों पर मर जाते हैं और जितना अधिक हम पूरे मर सकते हैं. यह एक वीडियो गेम में अलियासिंग के समान सिद्धांत है: जितना अधिक एक गोल आकार बनाने के लिए उपयोग किया जाता है उतना ही छोटा होता है और जितना कम हमें एहसास होता है.

ऊपर दिए गए उदाहरण में, यदि हम आंशिक रूप से मर जाते हैं, तो मरने की कुल संख्या (अच्छे और पूर्वाग्रह) पर हम 13 का अनुपात प्राप्त करते हैं.5 × 5 मिमी और 3 के मरने के मामले में 8 %.1 × 1 मिमी के मामले में 6 % मर जाता है. जितना छोटा मरता है, उतने ही वैध मर जाते हैं, किनारों पर हो सकता है, जिससे उपज बढ़ जाती है.

आप वेफर के केंद्र में एक बड़ा मरने का मिश्रण भी बना सकते हैं और अलियासिंग के कारण उपज का अनुकूलन करने के लिए किनारों पर छोटे मरने का उपयोग कर सकते हैं.

जेमी कहो, हम आयताकार पिस्सू बनाने के लिए राउंड वेफर्स का उपयोग क्यों करते हैं ?

खैर यह सिलिकॉन बनाने की विधि के कारण है जिसे czochralski प्रक्रिया कहा जाता है जो सिलिकॉन को सिलिंडर के रूप में देता है, देने के लिए बहुत ठीक स्लाइस में कटौती करता है वेफर्स.

दूसरा, उपज उन दोषों से प्रभावित होती है जो वेफर पर दिखाई दे सकते हैं. आप धूल के दाने के बारे में सोच सकते हैं जो वेफर पर गिरते हैं.

मैंने 0 की गलती घनत्व जोड़कर पिछले उदाहरण को फिर से शुरू किया.5 प्रति सेमी of. अब तुलना करें उपज निर्माण जो कार्यात्मक मरने की संख्या और उत्पादित उत्पादों की कुल संख्या के बीच के अनुपात से मेल खाती है. 5 × 5 मिमी की मृत्यु के मामले में, उपज 88 है.4 % जबकि 1 × 1 मिमी के साथ मर जाता है, उपज 99 है.5 %.

इसलिए इलेक्ट्रॉनिक पिस्सू के उत्पादन का अनुकूलन करने के लिए छोटे मरने के लिए यह दोगुना दिलचस्प है. फिर भी, कई छोटे चिप्स में एक जटिल चिप को काटने के लिए उनके बीच इन अलग -अलग चिप्स को संप्रेषित करने की आवश्यकता होती है, इसलिए हमें उन संचार तत्वों को जोड़ना चाहिए जो अतिरिक्त स्थान लेने और अतिरिक्त ऊर्जा का उपयोग करने के लिए आते हैं.

इसके अलावा, चिपलेट का उपयोग प्रदर्शन के साथ अंतिम चिप की लागत को संशोधित करने के लिए कार्यों के अनुसार उत्कीर्णन के विभिन्न चालाकी के मरने का उपयोग करना संभव बना सकता है.

अंत में, देखने के लिए एक और आर्थिक पहलू नई सुविधाओं को विकसित करने की जटिलता है. यह विशेष कंपनियों (या कम से कम स्टार्ट-अप्स स्टार्ट पर) के पास है, जो बौद्धिक संपदा ब्लॉक (फ़ंक्शंस) का उपयोग करने के लिए तैयार है. उदाहरण के लिए, एक प्रोसेसर निर्माता पीसीआई एक्सप्रेस, यूएसबी या डीडीआर कंट्रोलर्स जैसे कार्यों के लिए मरने के दौरान प्रोसेसर के विकास पर ध्यान केंद्रित करने में सक्षम होगा.

विभिन्न निर्माताओं से आने वाले चिपलेट की अंतर को सुविधाजनक बनाने के लिए, इंटेल, एएमडी, एआरएम, क्वालकॉम, सैमसंग या टीएसएमसी जैसे प्रमुख खिलाड़ियों ने चिपप्लेट, यूसीआईई के बीच एक संचार मानक बनाया हैयूनिवर्सल चिपलेट इंटरकनेक्ट एक्सप्रेस)).

दो उदाहरण: AMD और INTEL (ALTERTA)

एएमडी एपाइक

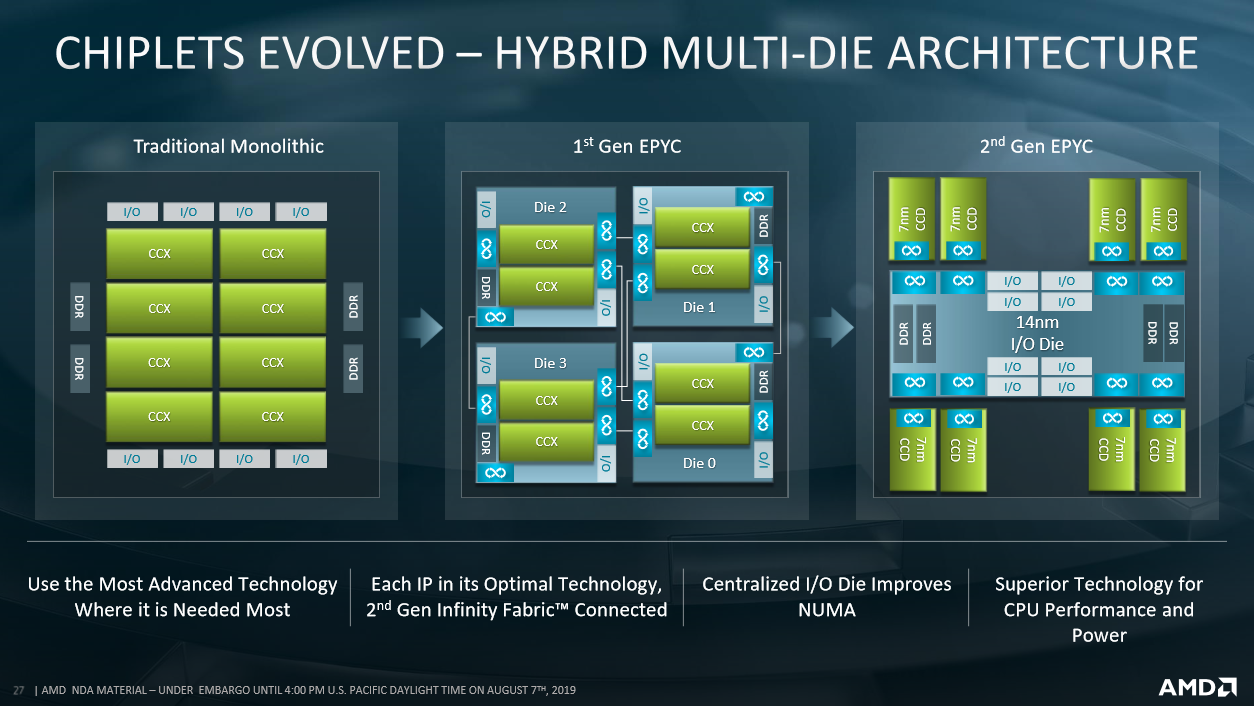

आज अधिक से अधिक प्रोसेसर इस चिपलेट तकनीक का उपयोग करते हैं. AMD EPYC प्रोसेसर की पहली पीढ़ी के बाद से चिपलेट का उपयोग करता है, जहां अलग -अलग दिलों को एक साथ जोड़ा जाता हैअनंत कपड़े.

EPYC प्रोसेसर की पहली पीढ़ी ने मरने का एक सेट देखा, जिसे पूर्ण प्रोसेसर के साथ एक साथ जोड़ा जा सकता हैअनंत कपड़े अंतिम प्रोसेसर बनाने के लिए. चिपलेट इसलिए एक प्रकार का छोटा स्वायत्त प्रोसेसर था: प्रत्येक मरने ने अपनी प्रविष्टियों/आउटपुट को प्रबंधित किया और इसका डीडीआर नियंत्रक था.

इन मर जाता है, या बल्कि चिपलेट, दो हैं कोर गणना जटिल (CCX, कैश मेमोरी के साथ चार कोर का एक सेट) के साथ -साथ एक DDR नियंत्रक, इनपुट/आउटपुट (उदाहरण के लिए PCI एक्सप्रेस) का प्रबंधन करता है और इसके लिए संचार मॉड्यूल हैंअनंत कपड़े.

छोटी सूक्ष्मता, पहली पीढ़ी के एपाइक पर हमेशा चार चिपलेट होते हैं. दिलों की संख्या को अलग करने के लिए, AMD CCX के अंदर दिलों को निष्क्रिय कर देता है. उदाहरण के लिए 24 कोर हैं, CCX में केवल 3 सक्रिय कोर हैं

इसलिए इस पहली पीढ़ी ने चिपलेट्स के सिद्धांत का उपयोग एक प्रकार की कॉपी/ग्लूड के रूप में किया, जो एक बड़े अखंड मरने के बजाय मर जाता है.

दूसरी पीढ़ी के लिए, एएमडी अवधारणा को थोड़ा आगे बढ़ाता है. वास्तव में, CCX अब स्वतंत्र हैं, जोड़े के भीतर जोड़े में समूहीकृत हैं कोर कम्प्यूट डाई (CCD) द्वारा जुड़ा हुआ है अनंत कपड़े DDR और प्रविष्टियों/निकास को प्रबंधित करने के लिए एक मरने के लिए मैं/ओ मर गया (Iod).

एएमडी पूरी तरह से कार्यों से अलगाव का शोषण करता है. वास्तव में CCD को 7 एनएम में उकेरा गया है जबकि IOD 14 एनएम में उत्कीर्ण है.

एक AMD प्रस्तुति के नीचे EPYC प्रोसेसर के चिपलेट्स में मार्ग को सारांशित करना.

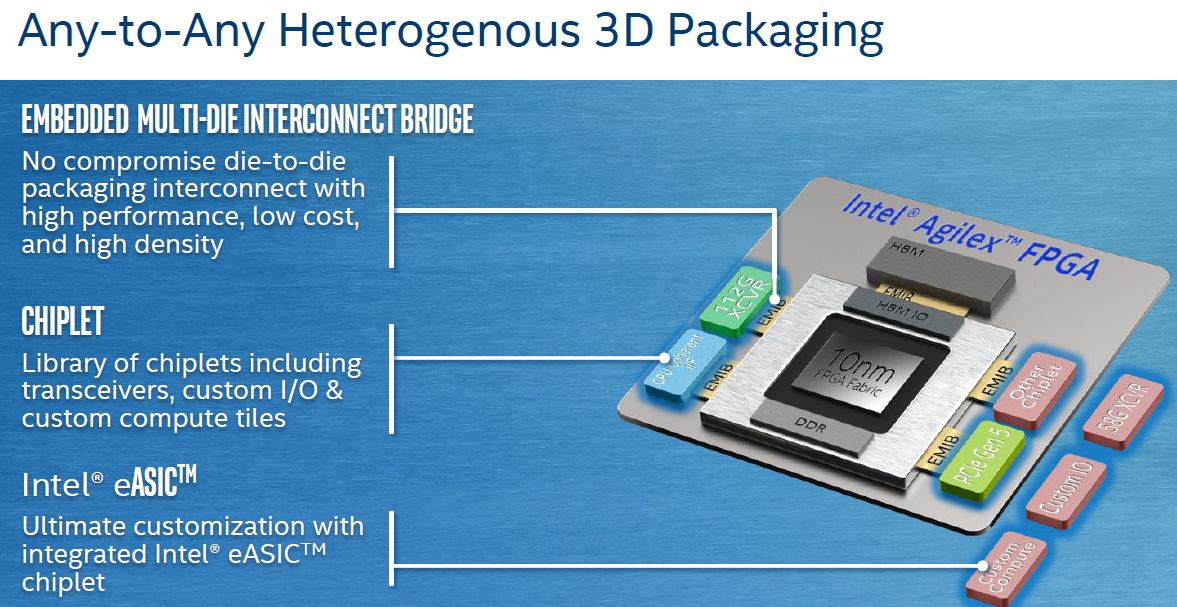

इंटेल एफपीजीए (परिवर्तन)

इंटेल प्रोसेसर हमेशा कुछ अपवादों को छोड़कर मोनोलिथिक चिप्स होते हैं जैसा कि हम इस लेख की शुरुआत में देख सकते हैं. फिर भी इंटेल FPGA (Reconfigurable FPGA) सेक्टर में नवीनतम पीढ़ी, Agilex के लिए चिपलेट का उपयोग करता है.

ये चिपलेट मुख्य रूप से उपयोग किए गए ट्रांसकेंस के प्रकार (फास्ट लिंक) की चिंता करते हैं और उन्हें कहा जाता है टाइल्स. यदि इंटेल इन टाइलों से पूर्वनिर्धारित रेंज प्रदान करता है, तो अपनी आवश्यकताओं के लिए अनुकूलित चिप्स होना संभव होना चाहिए.

टाइलें ट्रांससीवर्स की अधिकतम गति और समर्थित प्रोटोकॉल (ईथरनेट, पीसीआई एक्सप्रेस, आदि से विभाजित होती हैं।.): पी के लिए 16 जी, एच के लिए 28 जी, आर के लिए 32 जी, आदि।.

इंटेल भविष्य के लिए भी अनुकूलित चिपलेट को जोड़ने की संभावना को विकसित करता है जो अतिरिक्त कार्य प्रदान करेगा. वर्तमान में कंपनियों ने एक एडीसी/डीएसी (जेरिट टेक्नोलॉजीज) चिपलेट के साथ -साथ एक और ऑप्टिकल कनेक्शन (अयेर लैब्स) जारी किया है.

अंत में हमें यह विश्वास नहीं करना चाहिए कि चिप्स अखंड की मृत्यु हो चुकी है. उनके हमेशा फायदे होते हैं, विशेष रूप से आंतरिक संचार और विलंबता के संदर्भ में, जो कुछ अनुप्रयोगों के लिए महत्वपूर्ण हो सकता है जो बड़े -बड़े चिप्स की आवश्यकता होती है.

यह ब्रॉडकॉम और इसके स्विच 400g चिप्स का मामला है, जिनकी पसंद इस वीडियो में डिजाइनर द्वारा समझाया गया है: https: // www.यूट्यूब.कॉम/वॉच?V = b-cogmbaug4

मुझे उम्मीद है कि इस लेख में आपके पास और अधिक है और आपको वर्तमान चिप्स के निर्माण के बारे में थोड़ा और जानने की अनुमति दी. मैंने एक जटिल विषय को लोकप्रिय बनाने की कोशिश की, मुझे यह भी उम्मीद है कि मैं पहले पैराग्राफ के बाद आपको रखने में सक्षम था

एक टिप्पणी छोड़ने में संकोच न करें यदि कुछ बिंदु आपके लिए गुप्त हैं, तो मैं विवरण प्रदान करने का प्रयास करूंगा.

6 टिप्पणियाँ

यह उत्तर उपयोगी था

बहुत बढ़िया लेख, धन्यवाद @ zeql !

“मुझे भेड़ियों के लिए फेंक दो और मैं पैक वापस कर दूंगा.” – सेनेका

यह उत्तर उपयोगी था

मैं सोच रहा था कि चिपलेट्स का आगमन हार्डवेयर में एक निश्चित विकास पर विचार करने में सक्षम था (साथ ही उपभोक्ता ग्रेड वह सर्वर ग्रेड) भविष्य में, या यहां तक कि जिस तरह से हम उच्च और इष्टतम मशीनों को डिजाइन करते हैं, उस पर एक प्रतिमान बदलाव भी।.

कुछ अच्छी तरह से एकीकृत सिस्टम (विशेष रूप से Apple पर) केवल एक बहुत ही कुशल “क्लासिक” सीपीयू पर आधारित नहीं हैं, बल्कि कई विशेष सहायक चिप्स पर भी हैं जो सामान्यतावादी सीपीयू को उतारते हैं. स्मार्टफोन के रूप में एक सीमित प्रणाली में, हम H265 ट्रांसकोडिंग चिप्स पा सकते हैं, एआई के लिए गणना इकाइयाँ (सेब तंत्रिका इंजन) और निश्चित रूप से क्लासिक ग्राफिक इकाई.

इसलिए मैं 2 पीढ़ी के एएमडी एपिस के आरेख को लेता हूं और मुझे आश्चर्य है कि क्या चिपलेट्स पूरी इकाइयों से व्यावसायिक और औद्योगिक रूप से व्यवहार्य का उत्पादन करने का एक सरल तरीका होगा जो कुछ कार्यों पर इष्टतम प्रदर्शन प्राप्त करने के लिए कई विशेष चिप्स शुरू करते हैं।. उदाहरण के लिए, एक इकाई क्लासिक CCDs के लिए प्रदान कर सकती है, लेकिन एक DSP, एक GPU, Transco H265/AV1/VP9/…, AES, आदि करने के लिए एक चिप।. और यह सब IOD/इन्फिनिटी निर्माण के माध्यम से कनेक्ट करें. मशीनों/सर्वर के प्रत्येक निर्माता इसलिए अपनी रेडी-टू-यूज़ फाइनल यूनिट की रचना कर सकते हैं, जो कि खुद की रचना करके और बिना आर एंड डी/फ़ारामाइनुरस औद्योगिकीकरण की लागत के बिना हो सकता है.

यह मुझे APU की अवधारणा की याद दिलाता है, लेकिन मुझे नहीं पता कि क्या कोई रिपोर्ट है.

यह उत्तर उपयोगी था

मैं सोच रहा था कि चिपलेट्स का आगमन हार्डवेयर में एक निश्चित विकास पर विचार करने में सक्षम था (साथ ही उपभोक्ता ग्रेड वह सर्वर ग्रेड) भविष्य में, या यहां तक कि जिस तरह से हम उच्च और इष्टतम मशीनों को डिजाइन करते हैं, उस पर एक प्रतिमान बदलाव भी।.

कुछ अच्छी तरह से एकीकृत सिस्टम (विशेष रूप से Apple पर) केवल एक बहुत ही कुशल “क्लासिक” सीपीयू पर आधारित नहीं हैं, बल्कि कई विशेष सहायक चिप्स पर भी हैं जो सामान्यतावादी सीपीयू को उतारते हैं. स्मार्टफोन के रूप में एक सीमित प्रणाली में, हम H265 ट्रांसकोडिंग चिप्स पा सकते हैं, एआई के लिए गणना इकाइयाँ (सेब तंत्रिका इंजन) और निश्चित रूप से क्लासिक ग्राफिक इकाई.

इसलिए मैं 2 पीढ़ी के एएमडी एपिस के आरेख को लेता हूं और मुझे आश्चर्य है कि क्या चिपलेट्स पूरी इकाइयों से व्यावसायिक और औद्योगिक रूप से व्यवहार्य का उत्पादन करने का एक सरल तरीका होगा जो कुछ कार्यों पर इष्टतम प्रदर्शन प्राप्त करने के लिए कई विशेष चिप्स शुरू करते हैं।. उदाहरण के लिए, एक इकाई क्लासिक CCDs के लिए प्रदान कर सकती है, लेकिन एक DSP, एक GPU, Transco H265/AV1/VP9/…, AES, आदि करने के लिए एक चिप।. और यह सब IOD/इन्फिनिटी निर्माण के माध्यम से कनेक्ट करें. मशीनों/सर्वर के प्रत्येक निर्माता इसलिए अपनी रेडी-टू-यूज़ फाइनल यूनिट की रचना कर सकते हैं, जो कि खुद की रचना करके और बिना आर एंड डी/फ़ारामाइनुरस औद्योगिकीकरण की लागत के बिना हो सकता है.

यह मुझे APU की अवधारणा की याद दिलाता है, लेकिन मुझे नहीं पता कि क्या कोई रिपोर्ट है.

तो आपको पता होना चाहिए कि एक चिप अक्सर आईपी (बौद्धिक संपदा) के साथ की जाती है: एक फ़ंक्शन “ट्रांजिस्टर” स्तर पर काफी तैयार बेचा जाता है, लेकिन इसे इसके डिजाइन में एकीकृत किया जाना चाहिए.

एक क्लासिक उदाहरण ऑन -बोर्ड माइक्रोकंट्रोलर पर एक DDR3 नियंत्रक है. माइक्रोकंट्रोलर के निर्माता जरूरी नहीं कि DDR3 में महारत हासिल करें और एक DDR3 नियंत्रक बनाने के लिए कौशल, समय (न तो इच्छा) नहीं है. इसलिए वह एक नियंत्रक से एक आईपी खरीदता है और उसे अपने डिजाइन में एकीकृत करता है.

आपको एक आईपी और एक चिपलेट की संभावना के बीच अंतर को देखने में सफल होना होगा. मेरे लिए चिपलेट एक या एक से अधिक उन्नत सुविधाओं को लाने और लाने के लिए है और जो पहले से ही उत्कीर्णन के परीक्षणों को पार कर चुके हैं, इसलिए डिजाइन में एक अतिरिक्त कदम है. लेकिन सभी चिपलेट्स के साथ पूरी मिट्टी का परीक्षण करने की समस्या बनी हुई है. इसलिए हम लेगो की तरह सैकड़ों विविधताएं नहीं बना सकते. यह कम से कम आर्थिक वास्तविकता लेता है.

लेकिन हां, एक निश्चित मात्रा के लिए हम ला कार्टे सॉकेट्स बना सकते हैं.

बड़ा लाभ चिप के उत्पादन पक्ष पर है: यदि एक आईपी को अलग -अलग उत्कीर्णन चालाकी के लिए अस्वीकार किया जा सकता है, तो हमेशा अपने प्रारंभिक चालाकी में उत्कीर्ण होने के लिए सक्षम होने के लाभ के लिए एक चिपलेट (यदि यह पर्याप्त है) तो अन्य भागों चिप कर सकते हैं चिप कर सकते हैं छोटे उत्कीर्णन के साथ सुधार किया जाए.

यह उत्तर उपयोगी था

इसके अलावा मैंने सोचा था कि चिपलेट्स को एक मॉड्यूलर डिजाइन में इस्तेमाल किया जा सकता है. आप 4 चिप्स के साथ एक डिज़ाइन लेते हैं, दोषों के साथ fleas पूरे उत्पादन में वितरित किए जाते हैं, और 3 चिप्स वाले जो 4 पर काम करते हैं, वे नीचे एक सीमा होगी और 4 के साथ उन लोगों की तुलना में थोड़ा सस्ता होगा जो काम करता है.

जो पारंपरिक संचालन के संबंध में डिजाइन और औद्योगिकीकरण को सरल बनाता है.

मुफ्त सॉफ्टवेयर और GNU/लिनक्स फेडोरा वितरण के प्रेमी. #Jesuisarius

यह उत्तर उपयोगी था

इस दिलचस्प मेगा लेख के लिए धन्यवाद. मैं आपको प्रत्येक बिंदु का विस्तार करने के लिए बहुत अधिक समय प्यार करता हूँ कि आप ट्यूटोरियल में वास्तव में चीजों को समझने के लिए नहीं समझाते हैं लेकिन वैसे भी दिलचस्प हैं .

3 डी आईसी विषम एकीकरण के लिए मार्ग प्रशस्त करने में मदद करने के लिए चिपलेट डिज़ाइन किट का उपयोग करना

एक चिपलेट एक ASIC डाई है जो विशिष्ट रूप से डिज़ाइन किया गया है और अन्य चिपलेट्स के साथ संयोजन में एक पैकेज के भीतर ऑपरेशन के लिए अनुकूलित है. हेटेरोजेनस इंटीग्रेटेड (HI) में सिस्टम-इन-पैकेज (SIP) चिपप्लेट्स में इंटेगेंट मल्टीपल डाई या चिपलेट शामिल हैं. इन उपकरणों को विचार करने योग्य लाभ की पेशकश की गई, जिसमें प्रदर्शन, बिजली, क्षेत्र, लागत और टीटीएम शामिल थे.

चिपलेट डिज़ाइन एक्सचेंज (सीडीएक्स) में ईडीए विक्रेता, चिपलेट शामिल हैं

प्रदाता/असेंबलर और एसआईपी इंटीग्रेटर. यह वेबिनार चिपलेट डिज़ाइन किट (CDK) को 2 मानकीकृत करने में मदद करने के लिए प्रस्तुत करता है.5 डी और 3.डी आईसी डिजाइन एक खुला पारिस्थितिकी तंत्र बनाने के लिए.

सफल 2 के लिए एक पारिस्थितिकी तंत्र का निर्माण.5 डी और 3 डी चिपलेट मॉडल एकीकरण

एक एसओसी प्रक्रिया के समान, आपको चिपप्लेट्स के लिए एक पारिस्थितिकी तंत्र की आवश्यकता है. सामान्य बाजार अपनाने और चिपलेट आधारित डिजाइनों की तैनाती के लिए मुख्य सक्षम हैं:

- प्रौद्योगिकी: २.5 डी इंटरपोजिशन और 3 डी स्टैक्ड डाई मैन्युफैक्चरिंग एंड असेंबली प्रोसेस

- IP: मानकीकृत चिपलेट मॉडल

- वर्कफ़्लोज़: ईडीए डिज़ाइन फ्लो और पीडीके, सीडीके, डीआरएम और असेंबली रूल्स

- व्यवसाय मॉडल: चिपलेट मार्केटप्लेस

सीडीएक्स का प्रारंभिक फोकस 2 है.5 डी इंटरपोज़िंग-आधारित चिपलेट मॉडल 3 डी के साथ अनुसरण करने के लिए. वेबिनार में इन प्रयासों के बारे में अधिक जानें.

चिपलेट डिज़ाइन एक्सचेंज (सीडीएक्स) में ईडीए विक्रेता, चिपलेट प्रदाता/असेंबलर और एसआईपी इंटीग्रेटर्स शामिल हैं और एक चिपलेट इकोसिस्टम की सुविधा के लिए मानकीकृत चिपलेट मॉडल और वर्कफ़्लोज़ की सिफारिश करने के लिए एक खुला कार्य समूह है।. यह वेबिनार चिपलेट डिज़ाइन किट (CDK) को 2 मानकीकृत करने में मदद करने के लिए प्रस्तुत करता है.5 डी और 3.डी आईसी डिजाइन एक खुला पारिस्थितिकी तंत्र बनाने के लिए.

सफल 2 के लिए एक पारिस्थितिकी तंत्र का निर्माण.5 डी और 3 डी चिपलेट मॉडल एकीकरण

एक एसओसी प्रक्रिया के समान, आपको चिपप्लेट्स के लिए एक पारिस्थितिकी तंत्र की आवश्यकता है. सामान्य बाजार अपनाने और चिपलेट आधारित डिजाइनों की तैनाती के लिए मुख्य सक्षम हैं:

- प्रौद्योगिकी: २.5 डी इंटरपोजिशन और 3 डी स्टैक्ड डाई मैन्युफैक्चरिंग एंड असेंबली प्रोसेस

- IP: मानकीकृत चिपलेट मॉडल

- वर्कफ़्लोज़: ईडीए डिज़ाइन फ्लो और पीडीके, सीडीके, डीआरएम और असेंबली रूल्स

- व्यवसाय मॉडल: चिपलेट मार्केटप्लेस

सीडीएक्स का प्रारंभिक फोकस 2 है.5 डी इंटरपोज़िंग-आधारित चिपलेट मॉडल 3 डी के साथ अनुसरण करने के लिए. वेबिनार में इन प्रयासों के बारे में अधिक जानें.

लीक हुई छवि से GPU AMD Radeon के लिए चिपलेट के एक महत्वाकांक्षी डिजाइन का पता चलता है

लीक हुई छवि से GPU AMD Radeon के लिए चिपलेट के एक महत्वाकांक्षी डिजाइन का पता चलता है

- द्वारा

- खबर में

- 16 अगस्त, 2023 को

एक लीक हुई छवि सामने आई है, जो कि Radeon चिपलेट्स के साथ एक GPU डिजाइन का खुलासा करती है, माना जाता है कि NAVI 4C चिप 4C की एक रद्द परियोजना से. एक एकल GPU पर 13 और 20 अलग -अलग चिपलेट के बीच मौजूद डिजाइन, महत्वाकांक्षी AMD दृष्टिकोण की गवाही देता है. यह अधिक जटिल चिपलेट डिजाइन NAVI 31 सिलिकॉन से अलग है जो वर्तमान में Radeon RX 7900 XTX में उपयोग किया गया है. जबकि GPU के पिछले पुनरावृत्ति को पहली पीढ़ी माना गया था, इसने AMD के हालिया Ryzen प्रोसेसर की तरह एक वास्तविक चिपलेट डिज़ाइन का उपयोग नहीं किया था. हालांकि, NAVI 4C का खुलासा किया गया गर्भाधान एक महत्वपूर्ण अग्रिम का प्रतिनिधित्व करता है, क्योंकि इसमें कई गणना चिपलेट शामिल हैं, साथ ही एक सब्सट्रेट पर अलग -अलग I/O चिपलेट्स भी शामिल हैं. लीक हुई छवि 13 चिपलेट प्रस्तुत करती है, अतिरिक्त मेमोरी कंट्रोलर चिप्स की संभावना के साथ छवि पर प्रदर्शित नहीं किया जाता है.

छवि की प्रामाणिकता की पुष्टि करने के लिए, 2021 का एक प्रासंगिक पेटेंट समानांतर प्रोसेसर में मॉड्यूलरिटी की अवधारणा पर चर्चा करते हुए हाइलाइट किया गया है. पेटेंट पैटर्न लीक हुई छवि में दिखाए गए डिजाइन से मिलते -जुलते हैं, यहां तक कि अनुप्रस्थ कप के दूसरी तरफ अधिक चिपलेट की संभावना का सुझाव देते हैं.

दुर्भाग्य से, लीक हुई छवि में प्रस्तुत जीपीयू का डिज़ाइन रद्द कर दिया गया है. यह हाल के रिश्तों से सहमत है कि यह सुझाव देता है कि GPU की अगली पीढ़ी के लिए AMD का उच्चारण NAVI 43 और NAVI 44 मोनोलिथिक चिप्स पर होगा, जो आम जनता के लिए उच्चतर घटकों के बजाय है।. हालांकि, यह अनुमान लगाया जाता है कि एएमडी एक जीपीयू के विकास के लिए अपने प्रयासों को पुनर्निर्देशित करता है, जो कि आरडीएनए 5 के साथ संभावित रूप से ग्राफिक्स कार्ड के अपने भविष्य की सीमा के उच्च -खंड खंड के लिए कई गणना चिपलेट से बना है।.

यद्यपि गेम ग्राफिक्स के लिए कई गणना चिपलेट की प्राप्ति पारंपरिक सीपीयू गणनाओं की तुलना में अधिक जटिल है, अब डिजाइन बाधाओं को दूर करने और आरडीएनए 5 के लिए बेहतर समाधान पर काम करने के लिए एएमडी का निर्णय एक सकारात्मक कदम के रूप में माना जाता है. यह एएमडी के लिए एक बचाव योजना के लिए फायदेमंद होता, जैसे कि NAVI 31 के एक बेहतर संस्करण के लिए एक नया नोड.